Key Features for CXL AIC:

• Available in type 3 PCIe Gen5 Full Height, Half Length (FHHL) PCIe form factor.

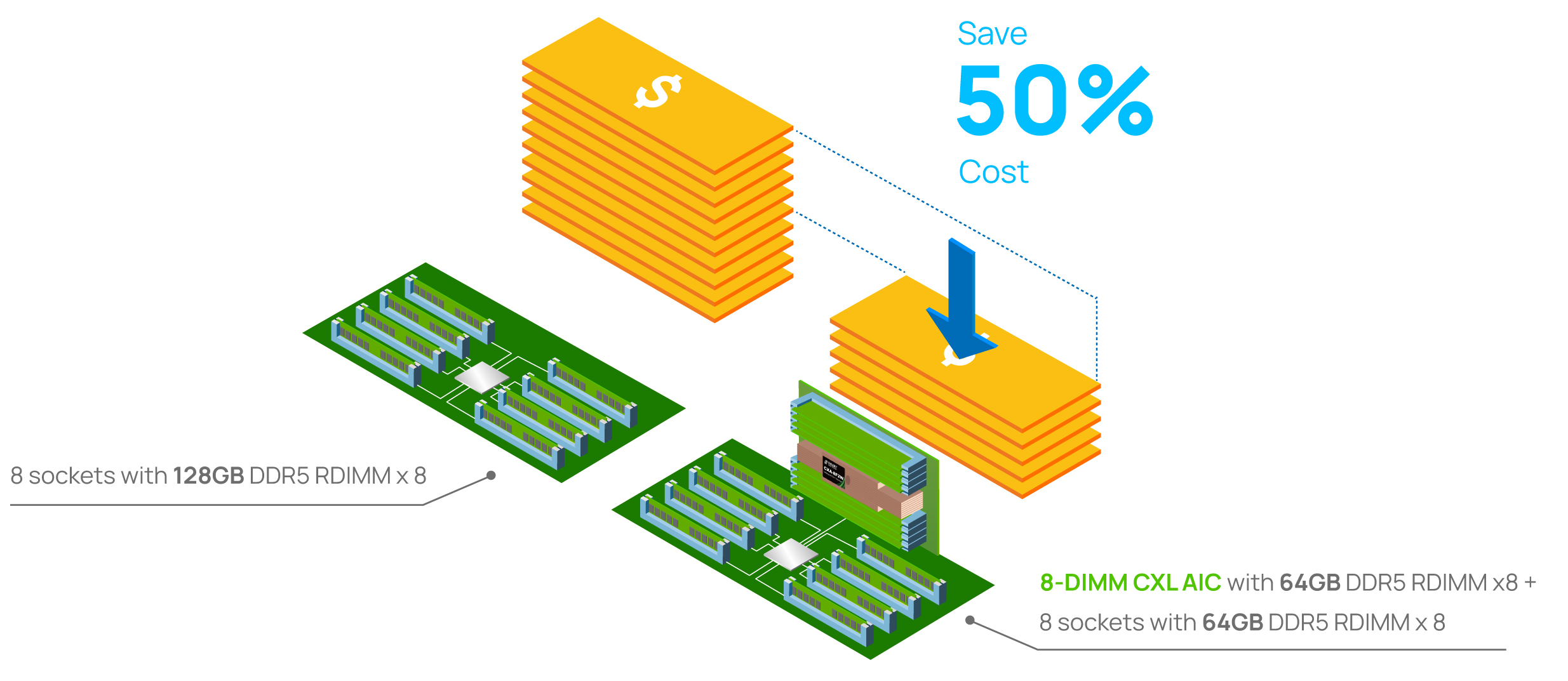

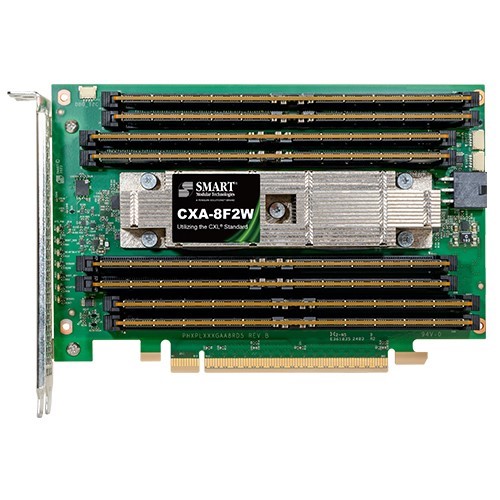

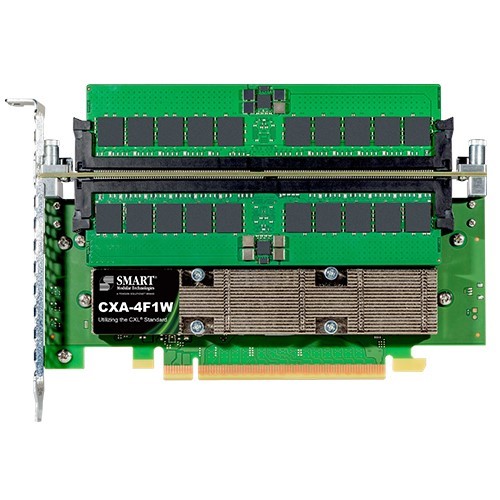

• The 4-DIMM AIC (CXA-4F1W) accommodates four DDR5 RDIMMs with a maximum of 512GB of memory capacity when using 128GB RDIMMs, and the 8-DIMM AIC (CXA-8F2W) accommodates eight DDR5 RDIMMs with a maximum of 4TB of memory capacity.

• The 4-DIMM AIC uses a single CXL controller implementing one x16 CXL port while the 8-DIMM AIC uses two CXL controllers to implement two x8 ports, both resulting in a total bandwidth of 64GB/s.

• The CXL controllers support “Reliability, Availability, and Serviceability” (RAS) features, and advanced analytics.

• Both offer enhanced security features with in-band or side band (SMBus) monitoring capability.

• To accelerate memory processing, these add-in cards are compatible with SMART’s Zefr™ ZDIMMs™.

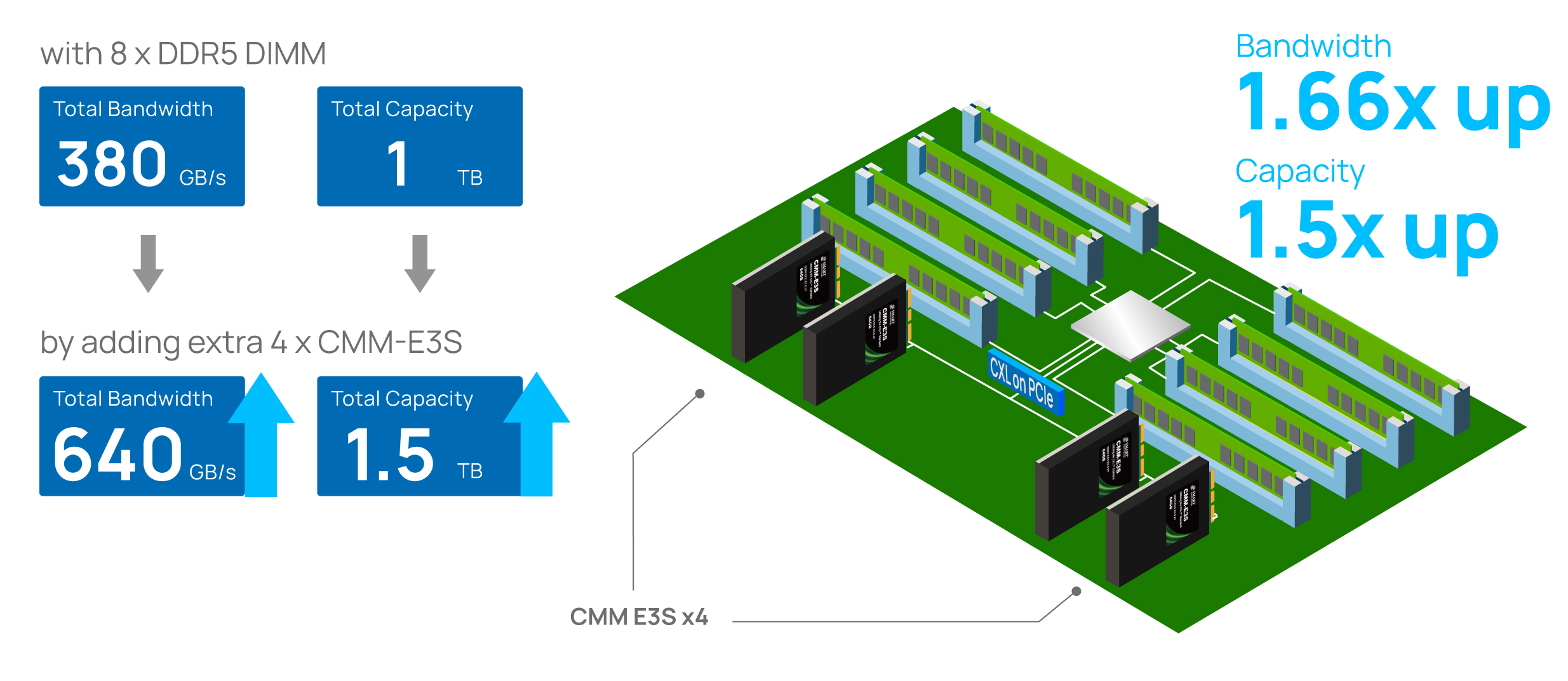

Key Features for CMM-E3S:

• Available in EDSFF E3.S 2T (2U Short) form factor

• CXL-2.0 compatible with PCIe Gen5 speeds running at 32GT/s

• Available in 64GB and 96GB densities

• Supports Reliability, Availability and Serviceability (RAS) features added in CXL 2.0

• Powered by only 12V supply from EDSFF compatible edge interface (SFF-TA-1009)

• Supports sideband interfaces for real-time debug, management and system update, enabling out-of-band management of the module

• Supports additional security features to protect data from side channel attacks